## PUFS – AN EXTENSIVE SURVEY

by

Yamini Ravishankar A Thesis Submitted to the Graduate Faculty of George Mason University in Partial Fulfillment of The Requirements for the Degree of Master of Science Computer Engineering

Committee:

|       | Dr. Jens-Peter Kaps,<br>Thesis Director                                                |

|-------|----------------------------------------------------------------------------------------|

|       | Dr. Kris Gaj,<br>Committee Member                                                      |

|       | Dr. Alok Berry,<br>Committee Member                                                    |

|       | Dr. Monson H. Hayes,<br>Chairman, Department of Electrical and<br>Computer Engineering |

|       | Dr. Kenneth S. Ball,<br>Dean, Volgenau School of Engineering                           |

| Date: | Summer Semester 2015<br>George Mason University<br>Fairfax, VA                         |

# PUFs – An Extensive Survey

A Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science at George Mason University

by

Yamini Ravishankar Bachelor of Technology SASTRA University, 2012

Director: Jens-Peter Kaps, Associate Professor Department of Computer Engineering

> Summer Semester 2015 George Mason University Fairfax, VA

Copyright © 2015 by Yamini Ravishankar All Rights Reserved

# DEDICATION

This is dedicated to my loving parents Shri. G.V. Ravisankar and Smt. S. Vijaya, beautiful sister Harini and my beloved fiancé Vasanth for their moral support and belief in me.

#### ACKNOWLEDGEMENTS

I would first like to thank my advisor Dr. Jens-Peter Kaps for giving me the opportunity to work on this thesis under him. Thank you for your valuable inputs and continuous guidance for the research and for your support during the schedule changes from my side.

I would also like to thank Dr. Kris Gaj for initially suggesting this research area for the course project in ECE646. Since then, the meetings with Dr. Kaps and Dr. Gaj have significantly improved my learning curve. The cryptography and hardware design courses helped me refine my analysis skills and thought process for approaching issues. Thank you all for molding me into the person that I am today.

I extend my sincere gratitude towards Dr. Alok Berry for being a mentor, and for his valuable advice at the personal, academic and professional levels.

I am really glad to have been part of the Cryptographic Engineering Research Group (CERG), and am thankful to all its members for the warm smiles and moral support to help get through the semesters. Thank you Bilal for your inputs and for helping me ramp up on PUFs initially.

A special thanks to Ms. Cynthia Ballentine for my first job as a Lab Assistant and being such a lovely person.

I am very grateful to my close friends, cousins and relatives for their words of hope and prayers and for always being there for me. I am also thankful to my laptop for putting up with me over the past six years during my under-graduate and graduate studies.

Finally, I extend my deepest gratitude towards God for guiding me like a polestar, through thick and thin and for keeping me grounded during success and failure.

# TABLE OF CONTENTS

| Page                                                |

|-----------------------------------------------------|

| List of Tables                                      |

| List of Figures ix                                  |

| List of Equationsx                                  |

| List of Abbreviations xi                            |

| Abstract xii                                        |

| 1. Introduction                                     |

| 1.1. Biometrics of Integrated Circuits              |

| 1.2. Why Unclonable?                                |

| 1.3. Applications of PUFs                           |

| 1.3.1. Key Generation and Storage                   |

| 1.3.2. Random Number Generators                     |

| 1.3.3. IP Protection                                |

| 1.3.4. Secure Microcontrollers and Processors       |

| 1.3.5. Radio-Frequency Identification Device (RFID) |

| 1.3.6. Hardware Obfuscation of Logic                |

| 1.3.7. Remote Attestation Schemes                   |

| 1.3.8. Vehicular Security                           |

| 1.3.9. Wireless Sensor Network Security             |

| 2. Physical-Unclonable Functions                    |

| 2.1. Basic Classification of PUFs                   |

| 2.2. PUF Constructions                              |

| 2.2.1. Silicon Based PUFs                           |

| 2.2.2. Ring-Oscillator Based PUF Constructions      |

| 2.2.3. ASIC-based PUF Constructions                 |

| 3. Evaluation of PUFs                               |

| 3.1. Need for Metrics                               |

| 3.2.   | Met   | trics Defined in Literature                                     | 23 |

|--------|-------|-----------------------------------------------------------------|----|

| 3.3.   | Not   | ations for the Metrics                                          | 24 |

| Hai    | nmir  | ng Distance                                                     | 24 |

| 3.4.   | Def   | inition of the Metrics – Device Axis                            | 25 |

| 3.4    | .1.   | Uniqueness                                                      | 25 |

| 3.4    | .2.   | Bit-Aliasing                                                    | 26 |

| 3.5.   | Def   | inition of the Metrics – Space Axis                             | 26 |

| 3.5    | .1.   | Uniformity                                                      | 26 |

| 3.5    | .2.   | Randomness                                                      | 27 |

| 3.6.   | Def   | inition of the Metrics – Time Axis                              | 27 |

| 3.6    | .1.   | Reliability                                                     | 27 |

| 3.6    | .2.   | Correctness                                                     | 28 |

| 3.6    | .3.   | Steadiness                                                      | 28 |

| 3.7.   | Eva   | luation Methodologies in Literature                             | 29 |

| 3.7    | .1.   | Evaluation of Metrics                                           | 29 |

| 3.7    | .2.   | Evaluation of Bit-Error Probabilities                           | 30 |

| 3.7    | .3.   | Estimation of Entropy                                           | 30 |

| 3.7    | .4.   | PUF System Model                                                | 30 |

| 4. Pos | t-Pro | cessing of PUFs                                                 | 32 |

| 4.1.   | Fac   | tors Affecting PUF Performance                                  | 32 |

| 4.1    | .1.   | Counteracting the Effect of Systematic Process Variations       | 32 |

| 4.1    | .2.   | Counteracting the Effects of Aging                              | 33 |

| 4.1    | .3.   | Counteracting the Effects of Noise and Environmental Variations | 33 |

| 4.2.   | Nee   | ed for Post-Processing of PUF Responses                         | 34 |

| 4.3.   | Hel   | per-Data Algorithms                                             | 34 |

| 4.3    | .1.   | Bit-Selection                                                   | 35 |

| 4.3    | .2.   | Entropy-Compression                                             | 35 |

| 4.3    | .3.   | Error-Correction                                                | 35 |

| 5. Att | acks  | on PUFs                                                         | 37 |

| 5.1.   | Ma    | chine Learning Attacks                                          | 37 |

| 5.2.   | Atta  | acks on PUF Interfaces                                          | 37 |

| 5.3.   | Side  | e-Channel Attacks                                               | 38 |

| 5.4.   | Helper-data Based Attacks                                | . 38 |

|--------|----------------------------------------------------------|------|

| 5.5.   | Repeatability Attacks                                    | . 38 |

| 5.6.   | Challenge-Based Attacks                                  | . 39 |

| 5.7.   | Scan-Chain Attacks                                       | . 39 |

| 5.8.   | Reverse-Engineering Attacks                              | . 39 |

| 5.9.   | Invasive Attacks                                         | . 39 |

| 6. Rin | g-Oscillator Based PUFs                                  | . 40 |

| 6.1.   | Need for Ring-Oscillator Based PUFs                      | . 40 |

| 6.2.   | Spartan6 FPGAs                                           | . 40 |

| 6.3.   | Configurable Ring-Oscillator Based PUF                   | . 45 |

| 6.4.   | CRO-PUF by Maiti et al                                   | . 46 |

| 6.5.   | CRO-PUF by Xin et al.                                    | . 47 |

| 6.6.   | FPGA-PUF based on Programmable LUT delays by Bilal et al | . 48 |

| 7. Pro | posed Configurable RO-PUF Design                         | . 49 |

| 7.1.   | Proposed Design                                          | . 49 |

| 7.2.   | Implementation                                           | . 49 |

| 7.3.   | Frequency Measurement                                    | . 50 |

| 7.4.   | Advantages of the Proposed Design                        | . 51 |

| 7.5.   | Results and Analysis                                     | . 51 |

| 7.5.   | 1. Data Collection                                       | . 51 |

| 7.5.   | 2. Datasets                                              | . 52 |

| 7.5.   | 3. Evaluation of Metrics                                 | . 53 |

| 8. A N | Novel Proposal for Post-Processing of PUF responses      | . 54 |

| 8.1.   | Biometrics                                               | . 54 |

| 8.2.   | Artificial Neural Networks                               | . 54 |

| 8.3.   | Hidden Markov Models                                     | . 54 |

| 8.4.   | Proposal for Post-Processing                             | . 56 |

| 8.4.   | 1. Advantages of this Method                             | . 57 |

| 8.4.   | 2. Concerns of this Method                               | . 57 |

| 9. Cor | nclusion                                                 | . 58 |

| 9.1.   | Open Questions and Future Research Directions            | . 58 |

| 9.2.   | Future Research Direction                                | . 59 |

|        |                                                          |      |

| 9.3.      | Conclusion | 59 |

|-----------|------------|----|

| Reference | ces        | 60 |

# LIST OF TABLES

| Table                                                                      | Page |

|----------------------------------------------------------------------------|------|

| Table 1. Notations                                                         |      |

| Table 2. Datasets analyzed                                                 |      |

| Table 3. Comparison of Metrics of predecessor designs with proposed design |      |

# LIST OF FIGURES

| Figure                                                                  | Page |

|-------------------------------------------------------------------------|------|

| Figure 1. Uniqueness of CRPs from two different ICs                     | 2    |

| Figure 2. Logic schematic of Anderson PUF cell                          | 10   |

| Figure 3. ALU PUF generating 4-bit responses                            | 10   |

| Figure 4. Basic arbiter PUF construction                                | 11   |

| Figure 5. High-level Buskeeper cell (left) and transistor level (right) | 12   |

| Figure 6. Buttefly PUF using cross-coupled latches                      |      |

| Figure 7. Examples of Composite PUF                                     | 14   |

| Figure 8. Schematic of DRAM PUF                                         | 15   |

| Figure 9. LR-PUF concept                                                |      |

| Figure 10. Basic Ring-Oscillator                                        |      |

| Figure 11. Ring-Oscillator PUF circuit                                  | 18   |

| Figure 12. a. Configurable RO,                                          | 18   |

| Figure 13. TERO loop                                                    |      |

| Figure 14. Dimensions for the metrics                                   | 23   |

| Figure 15. PUF system model                                             | 31   |

| Figure 16. Analogy to biometric identification                          | 31   |

| Figure 17. Four CLBs of Spartan6 showing the slices and carry chain     | 41   |

| Figure 18. SLICEX internal structure                                    | 42   |

| Figure 19. SLICEL internal structure                                    | 43   |

| Figure 20. SLICEM internal structure                                    | 44   |

| Figure 21. Configurable Ring Oscillator proposed by Maiti et al.        |      |

| Figure 22. Configurable RO-PUF by Xin et al.                            | 47   |

| Figure 23. FPGA-PUF based on Programmable LUT delays                    | 48   |

| Figure 24. Proposed Configurable RO-PUF                                 | 50   |

| Figure 25. Hidden Markov Model                                          | 55   |

| Figure 26. Proposed methodology using HMMs                              | 57   |

# LIST OF EQUATIONS

| Equation                                                 | Page |

|----------------------------------------------------------|------|

| Equation 1. Uniqueness [Mai12]                           |      |

| Equation 2. Uniqueness [HYKS10]                          |      |

| Equation 3. Bit-Aliasing                                 |      |

| Equation 4. Uniformity                                   |      |

| Equation 5. Randomness                                   |      |

| Equation 6. Reliability                                  |      |

| Equation 7. Correctness                                  |      |

| Equation 8. Relation between Reliability and Correctness |      |

| Equation 9. Steadiness                                   |      |

|                                                          |      |

# LIST OF ABBREVIATIONS

| Advanced Encryption Standard                            |          |

|---------------------------------------------------------|----------|

| Application Specific Integrated Circuit                 | ASIC     |

| Arithmetic Logic Unit                                   | ALU      |

| Artificial Neural Networks                              | ANN      |

| Butterfly PUF                                           | BPUF     |

| Built-In Self Test                                      |          |

| Configurable Logic Blocks                               | CLB      |

| Configurable RO-PUFs                                    | CRO-PUFs |

| Differential Sequence Coding                            |          |

| Dynamic Random Access Memory based PUF                  | DRAM-PUF |

| Error Correcting Codes                                  | ECC      |

| Field Programmable Logic Arrays                         | FPGA     |

| D-Flip-Flop based PUFs                                  | DFF-PUF  |

| Hamming Distance                                        | HD       |

| Hardware Intrinsic Security                             | HIS      |

| Helper Data Algorithm                                   | HDA      |

| Hidden Markov Model                                     | HMM      |

| Integrated Circuit                                      | IC       |

| Integrated Circuit Identification                       | ICID     |

| Intellectual Property                                   |          |

| Kendall Syndrome Coding                                 | KSC      |

| Look-Up Table                                           | LUT      |

| Longest Increasing Subsequence-based Grouping Algorithm | LISA     |

| Metal-Oxide Semiconductor Field-Effect Transistor       | MOSFET   |

| Non-Volatile Memory                                     | NVM      |

| Physical One-Way Function                               | POWF     |

| Physical One-Way Hash Function                          | POWHF    |

| Physical Unclonable Function                            | PUF      |

| Public-Key                                              | PK       |

| Radio-Frequency Identification Device                   | RFID     |

| Ring-Oscillator based PUFs                              |          |

| Sequential Pairing Algorithm                            | SPA      |

| Static Random Access Memory based PUF                   |          |

| Transient Effect RO-PUF                                 |          |

| Very Large Scale Integrated Circuits                    | VLSI     |

### ABSTRACT

PUFS - AN EXTENSIVE SURVEY

Yamini Ravishankar, M.S.

George Mason University, 2015

Thesis Director: Dr. Jens-Peter Kaps

Physical Unclonable Functions (PUFs) offer a promising solution to the issue of secure key generation on chips for cryptographic applications. For a given challenge, PUFs generate a response, unique to the device based on its inherent manufacturing variations, which is why PUFs are the biometrics of Integrated Circuits (ICs). Ring-Oscillator based PUFs (RO-PUFs) are a type of Silicon-based PUF that exploit the delay in interconnects and components of the design to generate unique keys. Configurable RO-PUFs (CRO-PUFs) reduce the number of ROs needed to generate a key of a given length compared to the RO-PUFs.

This thesis is an extensive survey of the history of PUFs – implementations and applications, and the evaluation, post-processing and attack methodologies. A CRO-PUF exploiting the delay of latches in the Configurable Logic Blocks (CLBs) of Spartan6 FPGAs was implemented on 20 Nexys3 boards. The statistical properties of the obtained responses indicated a Steadiness of 94.6% and a Uniformity of 46.7% respectively. A

novel proposal of using Hidden-Markov Models for post-processing of PUF responses for increased reliability is being made as a result of cross-disciplinary study of biometrics with hardware cryptography.

# 1. INTRODUCTION

The strength of any cryptographic implementation depends on the secrecy of the encrypting key or device identifier. Compromise on the secrecy of the key can result in the compromise of confidential information and breach of authentication protocol. Thus, the generation and storage of keys or identifiers is of prime importance to its security. Keys stored on non-volatile memory are vulnerable to attacks. Physical Unclonable Functions (PUFs) are the primitives which when implemented on Integrated Circuits (ICs) can generate unique and reliable keys without the need for secure storage on Non-Volatile Memories (NVM). Secure and low-cost key storage, unclonability, tamper resistance, randomness in responses are some advantages of using PUFs as security primitives.

### **1.1.** Biometrics of Integrated Circuits

Biometric authentication is a means of identifying individuals based on their inherent characteristics like DNA, fingerprints, iris, retina, voice, ear, face, or signature. These characteristics are unique to every individual and hence nearly impossible to clone.

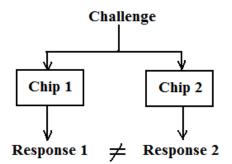

Similarly, silicon devices have unique inherent characteristics such as physical variations, frequency variations, etc. which can be exploited to uniquely identify them. A Physical Unclonable Function (PUF) is a challenge – response mechanism in which the mapping between a challenge (the stimulus) and the corresponding response (reaction of the PUF) is dependent on the complex and variable nature of the physical material. Unique Challenge-Response Pairs (CRPs) can be generated for the identification and

authentication of each IC, ie. the same challenge, when applied to different PUF instances, results in exclusive responses as shown in Fig.1. Thus, PUFs serve as the biometrics of Integrated Circuits.

Figure 1. Uniqueness of CRPs from two different ICs

The three main qualities that make PUFs analogous to Biometrics are individualism, inherency and unclonability [Mae12].

## 1.2. Why Unclonable?

Any system is said to be truly unclonable if it exhibits the properties of physical and mathematical unclonability. PUFs have an unpredictable way of mapping the challenges to the responses based to the structural disorder of the IC and hence are Physically Unclonable. This complex-interaction of the challenge with the random components in ICs results in stochastic Challenge-Response Pairs (CRPs) which cannot be modeled, thus leading to Mathematical Unclonability. Thus, a PUF is truly unclonable.

2

# 1.3. Applications of PUFs

Since their formal introduction in the early 2000s, the applications of PUFs in the field of hardware cryptography have increased manifold based on the different PUF constructions. I start this thesis with the many applications of PUFs proposed in literature to emphasize their importance.

# 1.3.1. Key Generation and Storage

Key generation and storage are indispensable in a vast majority of cryptographic implementations. The requirements for secure key generation and storage as given by [Mae12] are that

- a. Generated keys should be unique and unpredictable, and

- b. The memory that stores the keys should be reliable and must shield the keys from unauthorized access.

PUFs satisfy both these conditions because the randomness is intrinsically present in the device and the need for a protected non-volatile memory for secure key storage is avoided since keys can be generated on-the-fly and depend on the device. Another advantage is that PUFs are capable of generating keys for both symmetric and asymmetric cryptographic operations [SD07]. Thus, cryptographic key generation is a significant application of PUFs. A number of PUF based key generation techniques [TS06, GKST08, GSTK<sup>+</sup>09] have been proposed based on pattern matching [PD11], combination with fingerprints [HST10], recombination [YD10a].

# 1.3.2. Random Number Generators

Since the inherent nature of the PUF results in outputs that are random, PUFs could be used in random number generation. Some PUF based Random Number

Generators (RNG) have been implemented in literature [MNRS09, LSSTH12, AMSST10]. PUF-Pseudo-Random Functions (PUF-PRFs) were proposed in [AMSST10] for use as cryptographic primitives.

## 1.3.3. IP Protection

Intellectual Property (IP) protection is a major area of security research since any breach in the IPs of companies would lead to tremendous losses for the company. PUF protocols addressing the IP protection problem, with an emphasis on Public-Key cryptographic primitives have been proposed [GKST07a, GKST07b, GKST08]. Digital reconfigurable PUFs [ZP14] and PUF-Finite State Machine (FSM) based binding mechanisms [ZLLQ15] are also used to enforce IP protection.

### 1.3.4. Secure Microcontrollers and Processors

PUF implementations on ICs result in secure authentication and tamperresistance. Secure microcontrollers and processors have been implemented to test their functionality and use in [SDSD05, BHP11, MS12, HSKV13].

# 1.3.5. Radio-Frequency Identification Device (RFID)

The RFID technology embeds a chip on a physical object to uniquely identify the object. These have proven to be indispensable in applications including travel cards, identification cards, tracking of animals, and so on. The use of PUFs as RFID tags has been proposed and tested in [TS06, DSPSZK08, KKLSSW11] with the advantage of unclonability.

# 1.3.6. Hardware Obfuscation of Logic

Hardware obfuscation of logic is used for IP protection wherein PUF based logic can be configured as arbitrary logic to thwart IC reverse engineering. Signal path

obfuscation and direct replacement of arbitrary logic using PUFs are proposed for hardware obfuscation of logic [WP14]. This is a relatively new application for PUFs.

### 1.3.7. Remote Attestation Schemes

Remote Attestation is an authentication method for hardware and software using a remote server. This enables a remote system to determine the level of integrity of another system. PUFatt is a new lightweight remote attestation scheme impersonation attacks because of the hardware-software binding in Arithmetic Logic Unit based PUFs

### **1.3.8. Vehicular Security**

Vehicular security concerns with the IP protection in vehicles, modification of invehicle systems and its misuse with the normal vehicular operation in addition to the theft of the vehicle. [AGKT09] discusses in detail the application of PUFs for vehicular security, components identification and authentication.

### 1.3.9. Wireless Sensor Network Security

Wireless Sensor Networks (WSNs) provide a low cost solution to deploy large sensor arrays for military and civilian tasks. The storage and power limitations, unreliable communications and unattended operation pose security risks for the WSNs [LZLL14]. WSNs use Dynamic Random Access Memory (DRAM) as memory elements and hence [LZLL14] proposes the use of DRAM-PUFs for increasing security of WSNs.

PUFs can be used for licensing and certification applications and for building secure smart cards [GCDD02b], and also for remote services/features activation [GKST08].

Hence, the generation of a secure key/identifier from a PUF is a major concern since all applications make use of the intrinsic device variations. The security and

reliability of the generated key is of prime importance. Hence, a cross disciplinary study involving biometrics might lead to interesting methods of improving the statistical properties.

## 2. PHYSICAL-UNCLONABLE FUNCTIONS

The device mismatch between two ICs, based on the variations in the drain currents across an array of MOSFETs with common source and gate was proposed for IC Identification (ICID) [LDT00]. The basis for modern PUFs was laid by [Pap01] based on optically variable devices to derive unique and tamper-resistant identifiers at a very low cost. This work introduced the concept of physical one-way functions (POWFs) and physical one-way hash functions (POWHFs) as cryptographic primitives. It was later found that the intrinsically tamper-resistant microstructure of a medium's disordered structure can be converted to a fixed-length of binary digits for use as Physical One-Way Functions [PRTG02]. These led to the proposal for capitalizing on the inherent manufacturing variations of an Integrated Circuit as a Silicon Physical Unclonable Function (PUF) [LDT00, GCDD02b].

# 2.1. Basic Classification of PUFs

PUFs have been proposed on various technologies and materials. [Mae12] classifies the PUF constructions based on

- 1. Electronic nature of identifying features as

- a. Non-electronic PUFs wherein the non-electronic nature of materials is the basis for identification. For example optical PUFs,

- b. Electronic PUFs wherein the random variations in electronic characteristics like resistance and capacitance are used, For example, Silicon PUFs.

- 2. Construction property as

- a. Intrinsic PUFs which are inherently present in the device due to manufacturing variations [GKST07a], and

- b. Non-intrinsic PUFs wherein the PUF is externally evaluated or random features are explicitly introduced,

- 3. Security of challenge-response behavior as

- a. Strong PUFs wherein the CRP set size grows exponentially with the PUF size and

- b. Weak PUFs wherein the growth in the CRP set size is linear with the PUF size.

Intrinsic PUFs can be further classified based on their operating principles [Mae12] as

- Delay-based PUFs which measure the random variations on the delay of a digital circuit. This includes Arbiter-PUFs, Ring-Oscillator based PUFs and Glitch PUFs,

- Memory-based silicon PUFs which use random parameter variations called device mismatch. This includes Static Random Access Memory based PUFs (SRAM PUFs) and Dynamic Random Access Memory based PUFs (DRAM PUFs),

Mixed-signal circuits-based PUFs – which quantizes an analog signal to produce a digital response, for example, ICID – threshold voltage PUF and Inverter Gain PUF.

## 2.2. PUF Constructions

#### 2.2.1. Silicon Based PUFs

Silicon PUFs form a major class of subclass of electronic PUFs. These exploit the manufacturing process variations in the logic and interconnects present in a chip to derive the CRPs. The first practical realization of Silicon PUF was done in [GCDD02b]. The main advantage of using Silicon-based PUFs for cryptographic implementations is that they can be readily deployed in digital circuits on chips. The various silicon PUF constructions proposed in literature have been summarized below in an alphabetical order, with emphasis on Ring-Oscillator based PUFs.

### **Anderson PUF**

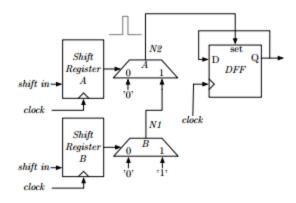

Anderson cells, as shown in Fig.2, form the primitives of the Anderson PUF [BBM15], a glitch based PUF. These cells produce logic-0 or logic-1 as output due to manufacturing variations only and do not require a challenge to generate a response. Thus, these can be used only for a single signature generation. The delay difference between the two pairs of shift-registers and multiplexers generates the glitch required for the operation of the Anderson PUF.

Figure 2. Logic schematic of Anderson PUF cell

#### Arithmetic Logic Unit Based PUF

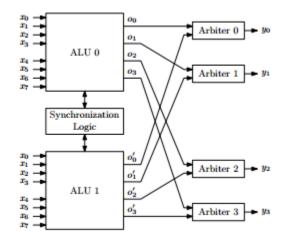

Arithmetic Logic Unit based PUF (ALU-PUF) [KKPSW14] is a novel PUF design based on the delay difference caused by manufacturing variations in two ALUs or other logic components available in a processor as shown in Fig. 3. This can be designed with a very low overhead when the redundant components in a processor are made use of. The design and working of the ALU-PUF is similar to that of the Arbiter PUF.

Figure 3. ALU PUF generating 4-bit responses

# Arbiter PUF

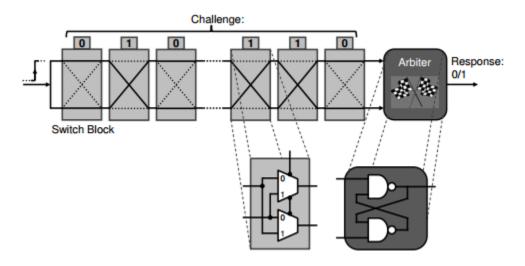

Arbiter PUF is a delay-based silicon PUF in which the output bit is determined by an arbiter circuit which resolves a race between two symmetrical digital paths in a circuit. When the circuit is designed to be perfectly symmetrical, the output bit of the arbiter is stochastic in nature and depends only on the manufacturing variations. [LLGSDD04] proposed the first Arbiter-PUF design implementation based on the delay paths between two switch blocks as shown in Fig.4.

Figure 4. Basic arbiter PUF construction

The two conditions required for the optimal design of an Arbiter PUF are given by [Mae12] as

- 1. Delay lines should be perfectly symmetrical and

- 2. Arbiter circuit should be unbiased

An asymmetric routing of the delay lines will lead to the circuit being biased towards a particular output bit since the signal passing through the shorter delay line would reach the arbiter faster. An arbiter-based PUF exploiting Programmable Delay Lines (PDL) to cancel out delay skews due to asymmetries in routing was proposed [MDK10]. The basic SR-latch was proposed for use in Arbiter PUF [LHKSB10] due to its symmetric construction and unbiased nature.

#### **Buskeeper PUF**

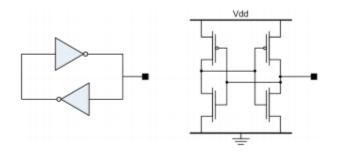

A Buskeeper is a weak latch with no control signals as shown in Fig. 5. On-chip buses with multiple drivers lead to an increased power consumption when these buses are in a floating state. Buskeepers prevent this scenario by maintaining the last driven state of the bus, when added to the circuit. It is functionally equivalent to a D-latch when Vdd is connected to the enable signal.

Figure 5. High-level Buskeeper cell (left) and transistor level (right)

Buskeeper PUF is a memory-based PUF construction using Buskeeper as primitives, similar to the D Flip-flop PUF (DFF-PUF) (described below). Experiments

[SSL12] prove that Buskeeper PUFs have a better reliability and uniqueness compared to DFF-PUFs and hence were proposed as their alternative.

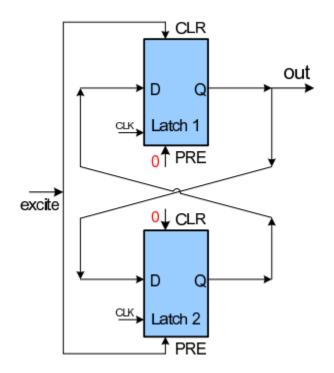

### **Butterfly PUF**

A cross-coupled circuit stores a bit value using a positive-feedback loop, and hence is widely used as building blocks of storage elements like latches, flip-flops and SRAM memories. The underlying concept of Butterfly PUF (BPUF) [KGMST08] is to design cross-coupled circuits in FPGAs which behave similar to SRAM cells. This was achieved by cross-coupling latches as shown in the Fig. 6

Figure 6. Buttefly PUF using cross-coupled latches

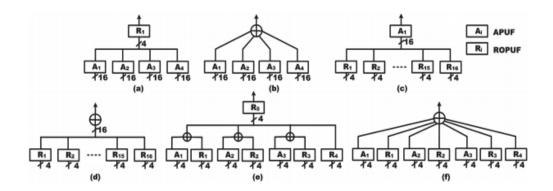

### **Composite PUF**

A composite-PUF [SSM14], constructed with smaller PUFs as building blocks has a larger challenge-space and superior quality metrics than its constituents. For example, Fig. 7 shows six composite PUF designs composed of Arbiter PUFs and Ring Oscillator based PUFs with 64-bit challenges and 1-bit response each.

Figure 7. Examples of Composite PUF

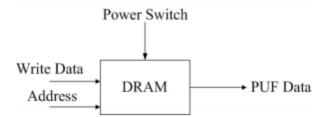

#### **DRAM PUF**

Dynamic Random Access Memory (DRAM) is a type of volatile memory. The decay time for the different bit storage elements vary due to manufacturing effects and this concept is being exploited for its use as DRAM PUFs [LZLL14]. DRAM cells are a main constituent of the Wireless Sensor Networks (WSN) and hence the DRAM-PUFs are proposed to provide a solution to the security issue of WSNs.

Figure 8. Schematic of DRAM PUF

### **Erasable PUF**

The concept of Erasable-PUFs was proposed in [DR14a]. These are Strong PUFs wherein single responses can be erased from the PUF without affecting any of the other responses. A proof-of-concept implementation is pending for this type of PUF.

# Flip-Flop Based PUF

The Flip-flop based PUF [MTV08] uses the powerup values of flip-flops of FPGAs similar to SRAM PUF. The main advantage of this type of PUF is that these can be implemented on FPGAs while SRAM PUF cannot because of the initial reset of SRAM-cells.

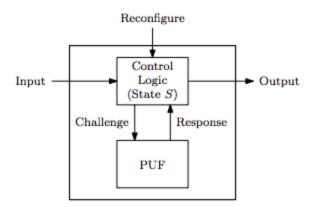

# Logically Reconfigurable PUF

In a Logically Reconfigurable PUF (LR-PUF) [KKLSSW11], the challengeresponse pairs depend both on the physical properties of the PUF and the logical state of a control logic. Dynamic reconfigurability is achieved by updating the state of the control logic.

Figure 9. LR-PUF concept

#### **Memristor PUF**

The relationship between the flux and electric charge in memristors are similar to the relation between voltages and currents in fundamental circuit elements. The process variation dependent switching delays form the basis of Memristor-PUF demonstrated in [MRF15] as a single-bit Memristor-PUF.

### **MRAM PUF**

MRAM is a nonvolatile magnetoresistive memory with a diverse range of applications. The unique energy-tilt resulting from the random geometric variations in the MRAM cells can be exploited as MRAM-based PUF with very high entropy [DSRBB15].

#### Quantum-Readout PUF

[Sko09] proposed a new type of security primitive – the Quantum Readout PUF (QR-PUF) which can be read out using quantum states, i.e. the challenge-response pairs are quantum states. It is based on the three physical assumptions namely – physical

unclonability, physical uniqueness and quantum-computational unclonability. [Sko13, SMP13] analyze the security of QR-PUF schemes. [SMP13] also focusses on challenge estimation attacks on QR-PUFs.

# **Reconfigurable PUF**

The concept of PUF primitives capable of transforming themselves into completely new PUFs, with challenge-response pairs different from that of the original PUF is called Reconfigurable PUFs (rPUFs) [KSSST09].

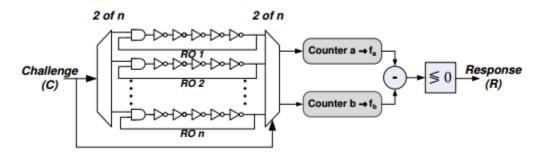

# Ring-Oscillator Based PUF

A basic ring-oscillator structure is shown in Fig. 10. The RO consists of an odd number of inverters connected in a loop which results in oscillations in the circuit. The frequencies of operation of two identical ROs vary due to process variations and are unique to each RO. This property of ROs is being exploited to implement the Ring-Oscillator based PUFs (RO-PUFs), proposed by [GCDD02b].

Even Number of Inverters Enable

Figure 10. Basic Ring-Oscillator

The RO-based PUF structure is shown in Fig. 11. An array of identical Ring-Oscillators implemented on a chip will have frequency variations unique to each RO. The frequency difference between pairs of frequencies is used to characterize the device and

to generate the unique ID. The oscillations produced by one RO influence the oscillations of another RO if they operate at the same time. Thus, frequency measurements are to be made by turning off all ROs other than the one being measured. Multiplexers and counters are used to select a particular RO and measure its frequency (number of oscillations).

Figure 11. Ring-Oscillator PUF circuit

Configurable ROs [Mai12] have multiple loops in the same RO structure which result in multiple configurations for a single RO. This results in a redundancy of responses which help increase the reliability of the circuit because the configuration with the highest frequency difference can be selected for measuring oscillations.

Figure 12. a. Configurable RO,

Figure 12. b. Selection of RO pair

Configurable RO-based PUF designs with chain-like mapping strategy [MS09b] for physical placement of oscillators offers a highly efficient solution for PUF reliability issue. An improvement over [MS09b] was proposed in [XKG11] which generates more IDs for the same area as used in the former. [MS11, MKS12] proposes compensation techniques (placement strategy and RO-pairs selection) to significantly improve the uniqueness and the CRPs of the RO-based PUFs. [HGK13] exploits the programmable delays of FPGA LUTs to generate additional bits of an identifier (ID) for a CRO-based PUF.

#### **SRAM PUF**

Static Random Access Memory (SRAM) is a memory technology that uses bistable circuits and is built with six MOSFET transistors. The start-up values in SRAMcells vary inherently and are exploited in the construction of SRAM-PUFs. These are the PUFs with commercially available applications because of their ease of implementation.

The drawback of using SRAM-PUFs is their vulnerability to physical attacks and high manufacturing cost. Various SRAM-based PUF constructions with varied applications have been proposed [GKST07a, GKST07b, GKST08]. describe different SRAM-PUF and Intrinsic PUF constructions respectively because of their presence in current FPGAs. [CDHS12] provides an analytical model for Start-Up Values (SUVs) of an SRAM PUF based on Static Noise Margin (SNM).

### Sense-Amplifier PUF

Sense-Amplifiers (SA) are clocked circuits that amplify very small differential voltages into full swing digital values. Variations in device characteristics of a sense amplifier result in a bias. These variations are used to build the Sense-Amplifier PUF with very low Bit-Error Rates [BM14].

#### **SuperPUF**

The concept of a SuperPUF [WYM14] is to integrate the on-chip entropy components distributed across the chip. This significantly reduces the wiring in the design resulting in low area overhead.

### 2.2.2. Ring-Oscillator Based PUF Constructions

#### **Inverter-Based RO-PUF**

The RO-based PUF utilizes multiple inverters (odd in number) to generate the oscillations. The inverter-based PUF [GLQ14] is a novel configurable RO-PUF framework which utilizes a single inverter to produce the oscillations, significantly reducing the hardware cost.

### Transient Effect RO-PUF

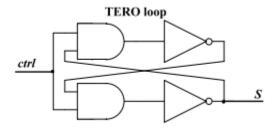

The Transient Effect Ring Oscillator (TERO) consists of an SR flip-flop with the S and R inputs connected to the same signal (here, ctrl signal), as shown in Fig. 13. Rising edge of the clock results in transitory oscillations in the TERO loop which stop after a short period of time due to intrinsic asymmetry. This phenomenon called oscillatory metastability is used for the construction of the TERO-PUF [BNCF13].

Figure 13. TERO loop

#### Ordering-Based RO-PUF

Sequential Pairing Algorithm (SPA) and Longest Increasing Subsequence-based Grouping Algorithm (LISA) are two effective secret extraction algorithms for RO-PUFs [YQ10]. PUFs in which the Grouping algorithms are used for error correction are called as Ordering-based PUFs. Ordering-based PUFs with the CRP enhancement schemes proposed in [KPD14] yield optimally robust and highly efficient PUF circuits with a large number of Challenge-Response Pairs [KPD15].

#### **ARO-PUF**

The aging-resistant RO-PUF [RFFT14] mitigates the effects of NBTI (Negativebias temperature instability) and HCI (Hot-Carrier Injection) by deactivating the PUF when it is not in use. This significantly reduces the aging of the PUF.

### 2.2.3. ASIC-based PUF Constructions

Fewer PUF implementations have been proposed on Application Specific Integrated Circuits (ASICs) than on FPGAs due to the high cost involved. [YMSD11, YSSMD12] evaluate an integrated ASIC implementation of a PUF-based key storage with integrated error correction.

[MV10, RWPK14] provide an extensive analysis of the available PUF constructions and reveal interesting future directions. [BH12] is a systematic overview of PUFs including the theoretical background, different silicon PUF realizations and issues pertaining to the implementation of PUFs in ICs. [HYKD14, RH14] provides a systematic survey on the implementations, attacks, error correction techniques and applications as security primitives for strong-PUFs and weak-PUFs. [CLB12, MRVKSL12] offer a comparative analysis of SRAM PUFs and D Flip-Flop based PUFs (DFF-PUFs) in the 65nm. Six different PUF constructions, including SRAM-PUF and Bus-keeper PUFs were implemented and compared using the silicon characterization vehicle [MRVKSL12].

# 3. EVALUATION OF PUFS

## **3.1.** Need for Metrics

Metrics are required to evaluate the performance of different types of PUFs and to standardize the security requirements expected from the PUFs.

# 3.2. Metrics Defined in Literature

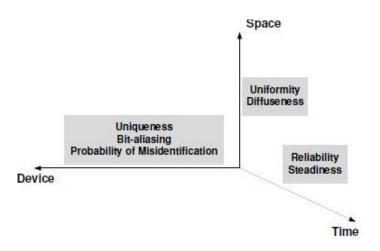

[Mai12, HYKS10] have proposed various metrics based on the statistical properties of the responses because binary PUF responses are obtained from every PUF irrespective of the technique used. [Mai12] proposed three dimensions for the PUF measurements along three axes namely device, space and time as shown in Fig. 14. The device axis captures the inter-chip variations in the PUF responses while the other two capture the intra-chip variations.

Figure 14. Dimensions for the metrics

The main metrics defined are

- Uniqueness

- Bit-Aliasing

- Uniformity

- Randomness

- Reliability

- Correctness

- Steadiness

# **3.3.** Notations for the Metrics

Table 1. Notations

| Ν | Total number of Chips analyzed                          |  |  |  |

|---|---------------------------------------------------------|--|--|--|

| n | Index of a Chip (range 1 to N)                          |  |  |  |

| Μ | Total number of ROs                                     |  |  |  |

| K | Total number of Identifiers (IDs) generated per<br>Chip |  |  |  |

| k | Index of an ID in a Chip (range 1 to K)                 |  |  |  |

| Т | Total number of Samples measured per ID                 |  |  |  |

| t | Index of a Sample (range 1 to T)                        |  |  |  |

| R | L-bit Response from the PUF                             |  |  |  |

| r | l <sup>th</sup> bit of the Response R                   |  |  |  |

## **Hamming Distance**

Hamming Distance (HD) between two responses is the number of bits that are different between the two responses. For example, the HD of two vectors that have the same values, eg. "1010" and "1010" is 0, while the HD of "1010" and "0101" is 4.

### **3.4.** Definition of the Metrics – Device Axis

#### 3.4.1. Uniqueness

Uniqueness is the average inter-chip Hamming distance (HD) computed across a group of chips. It gives an estimate of the inter-chip variation in terms of the PUF responses. Both Maiti et al. [Mai12] and Hori et al. [HYKS10] have defined uniqueness and their expressions only differ by a scaling factor.

According to Maiti et al., the uniqueness is given by

Equation 1. Uniqueness [Mai12]

Uniqueness =

$$\frac{1}{KL} \frac{2}{N(N-1)} \sum_{k=1}^{K} \sum_{l=1}^{L} \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} r_{i,k,l} \oplus r_{j,k,l}$$

According to Hori et al., the uniqueness is given by

Equation 2. Uniqueness [HYKS10]

$$\text{Uniqueness} = \frac{1}{KL} \frac{4}{N^2} \sum_{k=1}^{K} \sum_{l=1}^{L} \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} r_{i,k,l} \oplus r_{j,k,l}$$

The ideal value of uniqueness according to [Mai12] is 50%, which indicates that 50% of the bits between the PUF responses of any two different chips are different. The ideal value according to [HYKS10] is 100%. Discrete Cosine Transform (DCT) can be used in the post-processing of RO-PUFs [GI14] to de-correlate the RO outputs, to improve the uniqueness of the response and to increase the number of extracted bits.

### 3.4.2. Bit-Aliasing

Bit-aliasing [Mai12] estimates the bias of a particular response bit across several chips. It is defined as the Hamming-Weight of the l-th bit of the identifier across k-devices and is given by

**Equation 3. Bit-Aliasing**

$$(Bit - Aliasing)_{k,l} = \frac{1}{N} \sum_{n=1}^{N-1} r_{n,k,l}$$

The ideal value is 50% which means that the bit is neither biased towards a logic-1 nor a logic-0.

## 3.5. Definition of the Metrics – Space Axis

#### 3.5.1. Uniformity

For a response to appear random there should be an almost equal distribution of 1's and 0's in it. Thus, uniformity measures the proportion of 0's and 1's in the response bits of a PUF. Uniformity, as defined by [Mai12] is calculated as the percentage Hamming Weight of the n-bit response and is given by

**Equation 4. Uniformity**

Uniformity =

$$\frac{1}{KL} \sum_{k=1}^{K} \sum_{l=1}^{L} r_{n,k,l}$$

Ideal value for Uniformity is 50%, that is, there should be an equal number of logic-0 and logic-1 in a response for it to appear random.

#### **3.5.2. Randomness**

Randomness [HYKS10] is very similar to the Uniformity metric. Randomness indicates the balance of 0's and 1's in the response bits of the PUF. It is given by

#### **Equation 5. Randomness**

Randomness =  $-\log_2 \max(p_n, 1-p_n)$

where

$$p_n = \frac{1}{KTL} \sum_{k=1}^{K} \sum_{l=1}^{T} \sum_{l=1}^{L} r_{n,k,t,l}$$

The difference between Correctness and Randomness is that the latter also considers the distribution of response bits over T samples. The ideal value is 100%. [MN14] proposed the Random Patch Mixer (RPM) scheme as a solution to the issue of computational cost as well as to improve the frequency distribution randomness.

## 3.6. Definition of the Metrics – Time Axis

#### 3.6.1. Reliability

The reliability metric [Mai12] gives an estimate of how reliable the response bits are under varying operating conditions. It is the average value of the intra-chip Hamming Distance and is given by

Equation 6. Reliabililty

Reliability =

$$1 - \frac{1}{\text{KTL}} \sum_{k=1}^{K} \sum_{l=1}^{T} \sum_{l=1}^{L} r_{n,k,l} \oplus r_{n,k,t,l}$$

The ideal value for reliability is 100% which means that at any given time, the response bits should be constant. The reliability of the PUFs can be increased by

- a. Filtering out the unstable challenge-response pairs based on a stable response signal during the enrollment phase [DB14b],

- b. Offsetting the frequency values to be higher than a given threshold (Frequency-Offset algorithm [TLZ14]).

#### **3.6.2.** Correctness

Correctness [HYKS10] is a metric similar to reliability. It is defined as the sum of the Hamming Distances normalized by T, K and L. It also gives an estimate of how correct the response will be under different conditions. It is given by

**Equation 7. Correctness**

Correctness =

$$1 - \frac{2}{\text{KTL}} \sum_{k=1}^{K} \sum_{l=1}^{T} \sum_{l=1}^{L} r_{n,k,l} \oplus r_{n,k,t,l}$$

**Equation 8. Relation between Reliability and Correctness**

Correctness =  $(2 \times \text{Reliability}) - 1$

The ideal value is 100%.

#### 3.6.3. Steadiness

Steadiness [Mai12] refers to the degree of bias of a response bit towards '0' or '1'

over T samples. Steadiness is given by

**Equation 9. Steadiness**

$$\begin{split} \text{Steadiness}_n = \ 1 + \frac{1}{KL} \sum_{k=1}^{K} \ \sum_{l=1}^{L} \ \text{log}_2 \text{max}(p_n, 1-p_n) r_{n,k,t,l} \\ \text{where } p_{n,k,l} = \ \frac{1}{T} \sum_{l=1}^{T} \ r_{n,k,t,l} \end{split}$$

Ideal value of steadiness is 100% which means that the probability of any specific bit towards either logic-0 or logic-1 should be 1.

## 3.7. Evaluation Methodologies in Literature

[MRVKSL12] presents a Silicon Characterization Vehicle for a comprehensive experimental evaluation. [MMS09] analyzes the delay-based PUF implementations on FPGA. [YHMV12] evaluates the Advanced Encryption Standard (AES) S-box based Glitch PUFs on FPGAs. [YMSD11, YSSMD12] evaluates an integrated key generator ASIC implementation for cryptographic key generation. Built-In Self-Test (BIST) PUF [HMK14] is an online evaluation methodology for evaluating the unpredictability and stability of PUF identifiers with a very low overhead.

### 3.7.1. Evaluation of Metrics

[SKAH<sup>+</sup>11] evaluates the physical phenomenon that the initial state of a 6T-SRAM cell is highly dependent on the process variations. [MS11] proposes compensation techniques (placement strategy and RO-pairs selection) to significantly improve the uniqueness of the RO-based PUFs. [CLB12] provides a test framework for measuring reliability and uniqueness of PUFs. [SL12] investigates the reliability and uniqueness of

SRAM-PUFs on different technology nodes. [KKRSVW12] presents an evaluation methodology for assessment of the PUF properties - robustness and unpredictability.

### 3.7.2. Evaluation of Bit-Error Probabilities

A precise estimation of the bit-error probabilities is obtained based on the distribution of frequency measurements [HSP13] rather than the bit-errors after frequency comparison.

## 3.7.3. Estimation of Entropy

[BSL13] proposes a new method for accurate estimation of the entropy of Binary PUFs. A cross-disciplinary approach for obtaining statistically optimal entropy has been proposed in [KMNSVZ10]. The entropy of optical PUFs was estimated by the contexttree weighting method (CTW), a lossless compression and prediction algorithm in [ISSTW06].

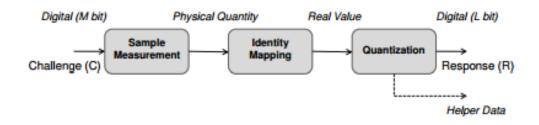

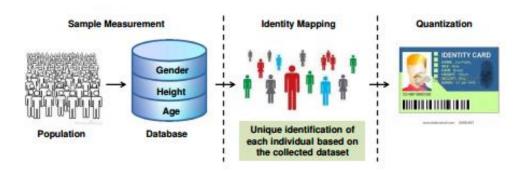

## 3.7.4. PUF System Model

Maiti, in his PhD. dissertation [Mai12] proposed an effective generic PUF system model [MGS12] to systematically optimize the quality factors as shown in Fig. 15. This divides the PUF into three components namely sample measurement, identity mapping and quantization. This is analogous to biometric identification as shown in Fig. 16. Sample measurement measures the process variation information from the individual chips. Identity mapping generates a unique identifier string for each chip. And quantization transforms the identifier into a binary string, which is the device identifier or key.

Figure 15. PUF system model

Figure 16. Analogy to biometric identification

Study of correlated process variations [MS09a], improvement of the existing RO-PUF design [MS09b, MMS09, MS11], PUF enhancement techniques [MKS12], characterization [MCHS10] of an RO-PUF over a large group of chips, study on the effect of aging on PUFs using accelerated aging [MDS11, MS13], PUF evaluationcharacterization technique [MGS13] for formal performance evaluation of the PUF, and a microprocessor intrinsic PUF [MS12] are the main contributions of [Mai12].

## 4. POST-PROCESSING OF PUFS

### 4.1. Factors Affecting PUF Performance

The main factors that affect the quality of the PUF responses are systematic process variations, aging, noise and environmental perturbations. Systematic variations on the chip result in deterministic process variations based on the location of the PUF on the chip, reducing the uniqueness of the chip. For example, in a RO-based PUF implementation, certain sections of the chip will have an average frequency lesser than the average at other locations. This is due to on-chip spatial process variations. Comparison of two frequencies between ROs in such areas will lead to non-stochastic responses. Aging of the chip results in irreversible circuit variations altering the circuit behaviour over time. This eventually leads to false-positive and false-negative responses. Negative bias temperature instability (NBTI), temperature-dependent dielectric breakdown (TDDB), hot carrier injection (HCI), and electro-migration are some Very Large Scale Integrated Circuits (VLSI) phenomena which accelerate aging on chips. Noise and environmental changes like variations in the operating voltage and temperature results in unstable bits, bringing down the reliability of the circuit [Mai12]. The methods proposed in literature to counteract the effects of these factors are summarized below:

### 4.1.1. Counteracting the Effect of Systematic Process Variations

[Mai12, DB14a] respectively propose the use of frequency difference between adjacent pairs of ROs and the use of relative frequencies to reduce the effect of

systematic variations on PUF response. This was demonstrated to have a significant improvement on the uniqueness and uniformity of the PUF responses. Entropy distillation extracts the entropy from the PUF responses from noise and systematic variations. [YQ13b, YQ14] propose a polynomial-regression based Entropy Distiller which decouples the systematic variations from required random variations by building a model for systematic variation. A Random Patch Mixer (RPM) scheme was proposed in [MN14] to mitigate the effects of systematic variations in RO-PUFs, wherein random numbers generated from a Random Number Generator are normalized to the maximum value of the RO frequency difference from the average RO frequency on chip. These normalized numbers, called as the Patch are added to the RO frequency for ID generation.

#### 4.1.2. Counteracting the Effects of Aging

The impact of aging on PUF characteristics have been examined in [MDS11, MRVKSL12, MS13] using accelerated aging tests. The aging-resistant RO-PUF [RFFT14] mitigates the effects of NBTI and HCI by deactivating the PUF when it is not in use. This significantly reduces the aging of the PUF circuitry.

### 4.1.3. Counteracting the Effects of Noise and Environmental Variations

Addition of two transistors to a regular inverter-based circuit causes the MOSFET transistors of the current-starved inverter circuit to operate in the subthreshold region. This results in a decreased delay of the inverter stage with increasing temperature. This positive temperature coefficient effect on current starved inverters was proposed for increased thermal stability to counteract the effect of negative temperature coefficient of

regular transistors [CZCC15]. Adapting the supply voltage ramp-up time to the ambient temperature reduces the noise on memory-based PUF responses [CHLMS13]. [BBM15] discusses the impact of voltage variation on the Anderson PUF implemented on Xilinx Spartan-3E. The temperature variation on PUF characteristics was studied in [MRVKSL12].

### 4.2. Need for Post-Processing of PUF Responses

The response bits obtained from a PUF cannot be used directly as a key, which demands high-entropy and reproducibility. Two main reasons for this are stated in [DV13a]:

- 1. The bits are not perfectly reproducible due to noise and environmental variations,

- 2. Statistical properties of some response bits might be undesirable, i.e. bias, correlations between responses or reduced entropy might exist.

Hence, to ensure the key generated from the PUF responses meets the requirements, post-processing is required.

## 4.3. Helper-Data Algorithms

The PUF responses are generally noisy random variables and can be referred to as the fuzzy secret. Helper Data Algorithms (HDAs), also called as Fuzzy Extractors or Shielding Functions are used to extract cryptographic keys from fuzzy secrets.

A detailed study of the currently existing Helper-Data Algorithms, threats due to their data leakage and manipulation and open problems was provided in [DGSV15]. Softdecision information, wherein the bit reliabilities are used to determine the secret key from the noisy input, was proposed to improve the efficiency of Helper Data Algorithms

for SRAM-PUF responses in [MTV09a, MTV09b, SL12]. [GSTK<sup>+</sup>09] investigated the properties of Fuzzy Extractors and Helper Data algorithms to securely deploy secret keys to a low cost wireless node. [BGSST08] presents hardware-resource efficient Fuzzy Extractor implementations on FPGAs. Sequential Pairing Algorithm (SPA) and Longest Increasing Subsequence-based Grouping Algorithm (LISA) are two effective secret extraction schemes for RO-PUFs [YQ10]. Reverse fuzzy extractors [HKMP<sup>+</sup>12] are efficient for extremely lightweight implementations.

The three main components of a HDA are bit selection, error-correction and entropy compression.

#### 4.3.1. Bit-Selection

The first step in HDAs is bit-selection, wherein the least reliable bits are discarded to reduce the complexity of the error-correction.

#### 4.3.2. Entropy-Compression

Correlations and bias of the PUF responses and leakage of HDA information result in non-maximum entropy. Entropy compression or privacy amplification ensures the uniformity of key and preserves the entropy of the response by increasing the ratio of input to output bits. Hash functions are generally used for entropy compression.

### 4.3.3. Error-Correction

Error-correction schemes are used in HDAs to ensure that the generated keys are reproducible.

The different error-correction constructions in literature have been compiled in [DGSV15]. It includes

- Temporal Majority Voting which uses majority voting for reconstruction of the responses,

- 2. Exhaustive search for searching error patterns, but is resource-intensive,

- Secure-Sketch commonly used in HDAs. Code-offset and Syndrome based constructions are the common Secure-sketch constructions,

- Codes in parallel non-overlapping sections of the response are processed independently to reduce the decoding complexity,

- Concatenated codes concatenation of two ECCs is capable of correcting many errors while maintaining entropy,

- Soft-Decision decoding depends on bit-reliabilities for decoding and has better error-correcting capabilities compared with Hard-decision decoding techniques,

- Convolutional codes have smaller code-words compared to block codes and are easier to implement, for example – Viterbi algorithm,

- Substring matching error patterns are detected by a substring search for errors in the response.

[YMDV13] provides an overview of the Syndrome Coding schemes proposed for post-processing of the PUF responses. The various error-coding schemes in implementations include Index-based Syndrome Coding [YD10b], Compressed Differential Sequence Coding [HS14], Bose-Chaudhuri and Hocquenghem (BCH) coding [KHKHI14a], Systematic Low Leakage Coding scheme (SSLC) [HYP15], Kendall Syndrome Coding (KSC ) [KPD14, KPD15].

## 5. ATTACKS ON PUFS

### 5.1. Machine Learning Attacks

Machine learning attacks are implemented on PUFs by building models which determine the internal parameters of PUFs. Modeling attacks [RSSDDS10, RSSX<sup>+</sup>13] are used to test the resilience of strong PUF designs. [HMV12] uses machine learning to introduce modeling attacks on 65 nm Arbiter PUFs. [RS14] is a detailed study on machine-learning based modeling attacks on strong PUFs and proposes suggestions for increasing the security of strong PUFs. Evolution Strategies (ES)-based machine learning techniques can successfully attack PUFs even if direct challenges and responses are not available [Beck15], thus increasing the vulnerability of highly obfuscated PUF responses. This has been demonstrated with successful attacks on reverse-fuzzy extractors. The Composite PUF is vulnerable to cryptanalysis and modeling attacks [SNMC15] when the independence of its components is exploited. Simulated results for a PUF design based on non-linear voltage transfer characteristics demonstrate improved machine-learning attack resistance in PUFs [VK15].

## 5.2. Attacks on PUF Interfaces

The assumption in most PUF designs in literature is that an adversary cannot modify or enhance a PUF interface in a "bad" way. Thus the vulnerability of PUF interfaces towards attacks and solutions are proposed in [DR14b].

www.manaraa.com

# 5.3. Side-Channel Attacks

Side-channel attacks are a subset of physical attacks wherein the attacker gains information during the operation of the device and uses it for cryptanalysis. They are easy to implement and pose a serious threat to the security of cryptographic implementations. [Sch10] provided an extensive study on the side-channel analysis of PUFs. [XB14] proposed taxonomy of the different side-channel attacks on PUFs with a complete study on the challenges and countermeasures for the same. Arbiter-PUFs are prone to machinelearning modeling attacks when the challenge-response pairs are known to the attacker. Controlled PUFs overcome this issue because the direct challenge-response pairs are never revealed. However, a hybrid side-channel analysis along with machine-learning can enable an attacker to perform both active as well as passive side-channel attacks on controlled-PUFs [BK14]. A study on the physical vulnerabilities of PUFs [HBNTS14] shows that most SRAM-PUF implementations available in market as a replacement for non-volatile memory key-storage lack sufficient protection against physical attacks.

# 5.4. Helper-data Based Attacks

PUF-based pattern matching key generators are vulnerable against the manipulation of public helper data [DV13a]. [DV14b] exposes the vulnerability of sequential pairing algorithm, group-based RO-PUFs and entropy distiller constructions for key-recovery based on helper-data.

# 5.5. Repeatability Attacks

Environmental deviations induce faults in Arbiter and RO-based PUFs, resulting in repeatability attacks [DV13b]. The 65nm CMOS Arbiter PUFs can be modelled successfully by exploiting the response repeatability [DV13c]. Repeatability attacks on

Arbiter-PUFs and RO-PUFs by increasing the fraction of unstable CRPs were studied in [DV14a].

## 5.6. Challenge-Based Attacks

Challenge estimation attacks are used for the analysis of the security of QR-PUFs [Sko13]. The increased number of CRPs in [MKS13] is prone to cryptanalytic attacks because the responses to different challenges are not independent, and along with the helper data, can be used to predict responses to unknown challenges with a high probability of success.

# 5.7. Scan-Chain Attacks

A generic procedure for testing Fuzzy Extractors was proposed [CRHN14] which also helps prevent scan-chain abuse for attacks.

## 5.8. Reverse-Engineering Attacks

Reverse engineering is the process of reproducing a circuit functionality based on the extracted knowledge. Hardware obfuscation of logic [WP14], covert indices and random subsets of the PUF response strings [RMKWD14] and gate- level characterization of the PUF in a sequential PUF architecture [WWNP14] exhibit resilience to functional reverse-engineering of the PUF.

## 5.9. Invasive Attacks

Invasive attacks are the attacks on PUFs which causes irreversible changes in the circuitry. Controlled PUFs (CPUFs) [GCDD02a], Reconfigurable PUFs (rPUFs) [WWNP14] and PUF-PRFs [AMSST10] exhibit resilience against invasive physical attacks.

### 6. RING-OSCILLATOR BASED PUFS

### 6.1. Need for Ring-Oscillator Based PUFs

The start-up values of memory cells are used for the generation of key in some memory-based PUFs, for example SRAM-PUF. Modeling attacks on these memory-based PUFs are possible if the memory-cell values are compromised. The delay-based PUFs generate keys on-the-fly and do not require the key to be stored in a non-volatile memory and hence offer more security than memory-based PUFs. The Arbiter PUF, a delay-based PUF described in Chapter 3, requires that the design be highly symmetrical to ensure that the output is dependent on the process variations and also to ensure unbiased results. A highly symmetric design for an Arbiter PUF requires rigorous placement and routing and is nearly impossible on an FPGA. In contrast, for the Ring-Oscillator based PUF design, the basic Ring-Oscillators which have to be identical can be easily implemented on FPGAs and are thus preferred over Arbiter-based PUFs.

### 6.2. Spartan6 FPGAs

Field Programmable Gate Arrays (FPGAs) are re-programmable semiconductor devices which can be programmed according to the design requirements. They consist of a matrix of Configurable Logic Blocks (CLBs) connected through programmable interconnects. The major manufacturers of FPGAs are Xilinx, Altera and Actel.

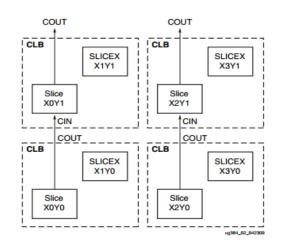

The CLBs are the logic resources in an FPGA wherein the design is implemented. In Xilinx Spartan6 FPGAs, each CLB consists of two slices – SLICEX and

SLICEM/SLICEL as shown in Fig. 17. The slices in the bottom-left corner of CLBs consist of alternating SLICEM and SLICEL while the ones on the top-right corner are the SLICEX. Each CLB is connected to a Switch Matrix and the slices in a CLB do not have direct connections with each other.

Figure 17. Four CLBs of Spartan6 showing the slices and carry chain

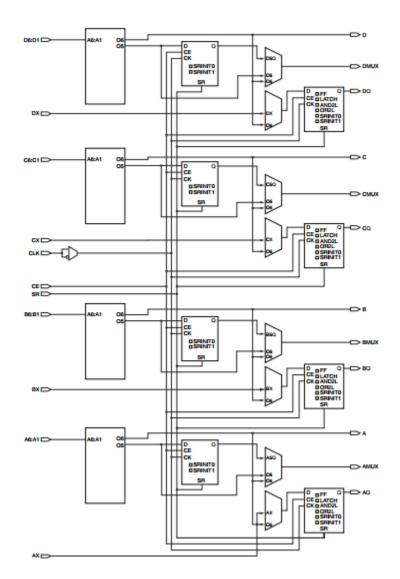

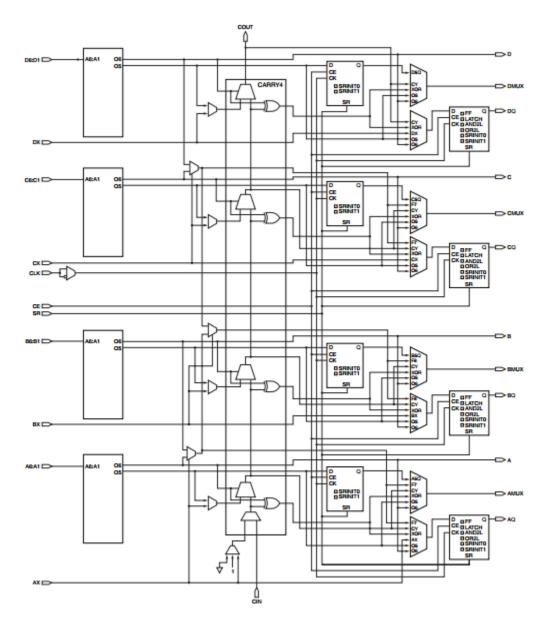

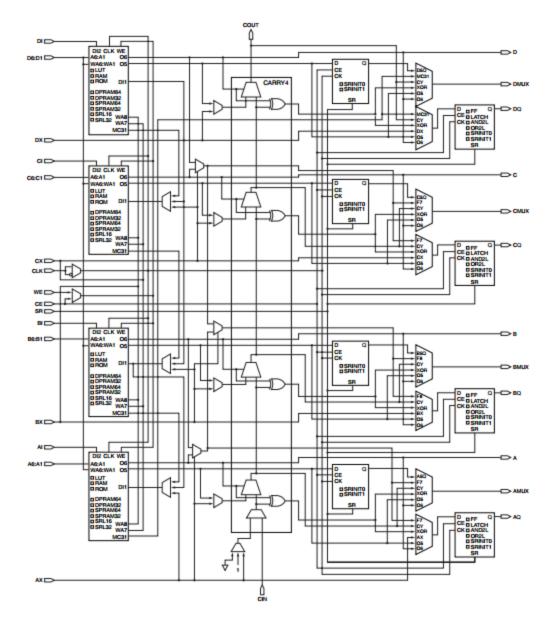

Every slice consists of eight storage elements and four look-up tables. SLICEX (Fig. 18) is the basic slice of the three. SLICELs (Fig. 19) contain an arithmetic carry structure in addition to the basic components along with wide-function multiplexers. SLICEMs (Fig. 20) have the additional capability of using the LUTs as distributed RAM and variable-length shift registers.

Figure 18. SLICEX internal structure

Figure 19. SLICEL internal structure

Figure 20. SLICEM internal structure

# 6.3. Configurable Ring-Oscillator Based PUF

Multiple configurations for a single RO is the essence of CRO-PUFs, as described in Chapter 3. The different configurations could be used to generate higher number of bits per RO. The highly reliable configurations could be used for applications by masking the configurations with unsteady bits. For calculating the frequency difference of two ROs, care should be taken to ensure that both the RO are operating in the same configuration. This is important because different configurations have different wire-lengths and would lead to biased outputs.

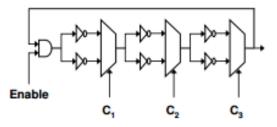

### 6.4. CRO-PUF by Maiti et al.

The Configurable Ring-Oscillator proposed in [Mai12] fits into a single Configurable Logic Block as shown in the Fig. 21. The main advantage of restricting a design to a single CLB is that it can be defined as a macro and duplicated with identical routing leaving the frequency variation only to the physical variations.

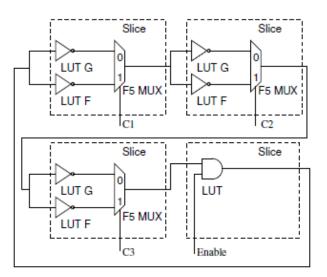

Figure 21. Configurable Ring Oscillator proposed by Maiti et al.

A single RO makes use of three slices with two Look-Up Tables each to function as inverters and the fourth slice is used as an enable switch for the RO. The internal MUXes in the CLB Slices are used to select either LUTG or LUTF with select signals C1-C3. Thus the design has eight different configurations. When the select signals are used as challenges, we get eight CRPs from a single RO compared to one CRP in a basic RO. When a value of "000" or "111" is given to the select signals, they represent the basic ring-oscillator.

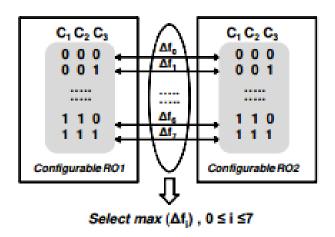

### 6.5. CRO-PUF by Xin et al.

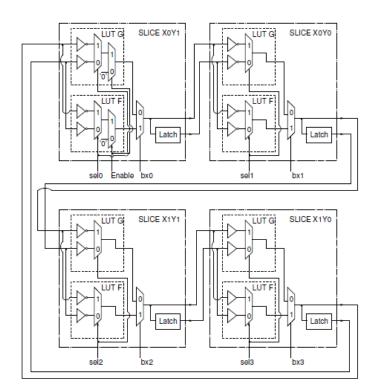

The CRO-PUF model proposed in [XKG11] is based on [Mai12]. This design has a higher number of configurations compared to [Mai12] and utilizes the latches available in the FPGA CLBs to add delays on the RO as shown in Fig. 22. Each RO was implemented on a single CLB of Spartan3 FPGAs which consists of 4 slices each.

Figure 22. Configurable RO-PUF by Xin et al.

This design has 256 possible configurations for each configurable RO and still fits into a single CLB block. The select signal bx selects which LUT should be used in the ring while the *selx* signals decide whether the latch of the previous slice is included in the ring. This model results in a lower frequency compared to the [Mai12] because of the inclusion of the latches.

## 6.6. FPGA-PUF based on Programmable LUT delays by Bilal et al.

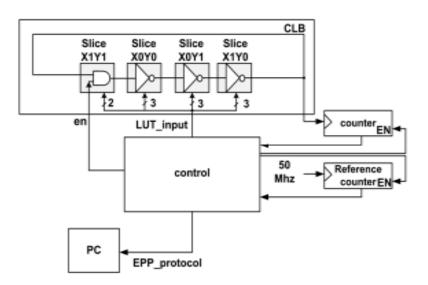

The CRO by Bilal et al. [HGK13] was designed on Spartan3E devices. Each RO consists of three inverters and an AND gate as shown in Fig. 23, and fit in a single CLB of the FPGA. The inverters are configured in the LUTs of the CLB. 130 ROs were implemented on each chip with 8 configurations each. Hence the number of response bits generated is 1032 bits. The difference of this design with the previous two is that in this, the path outside the LUTs remains constant, minimizing the impact of routing and wire delays on oscillator frequency. This exploits the inherent randomness in the LUTs to derive the ID.

Figure 23. FPGA-PUF based on Programmable LUT delays

## 7. PROPOSED CONFIGURABLE RO-PUF DESIGN

## 7.1. Proposed Design

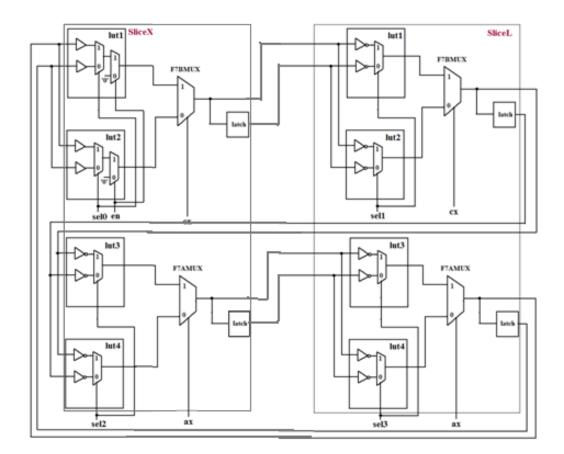

The proposed Configurable RO-PUF model (Fig. 24) is an adaptation of Xin's design [XKG11] on Spartan6 FPGAs and consists of 256 configurations. Each individual RO is implemented on a single CLB utilizing a total of 8 LUTs of SLICEX and SLICEL or SLICEM. The first SLICEX is implemented with buffer such that the total number of inverters in the design is odd. The *en* signal is used to enable the Ring-Oscillator. The MUXes external to the LUTs select the path through a particular LUT while the internal MUXes in LUTs select whether the delay due to the latches are taken into consideration. This inclusion of latch in the RO differentiates Maiti's work from Xin's design and this proposed design with increased number of configurations. The main difference between this design and Xin's implementation is that this was implemented on 2 slices with 4 LUTs each while Xin's design was implemented on 4 slices with 2 LUTs each.

# 7.2. Implementation

The PUF design was implemented on Spartan6 FPGAs present in the Nexys3 boards with 64 ring oscillators. The design was tested on 20 boards and the frequency data was collected.

Figure 24. Proposed Configurable RO-PUF

### 7.3. Frequency Measurement

The frequency of the selected RO is obtained by using two counters – one for counting the rising edges of the RO and the other driven by a crystal of 50 MHz. The RO-counter value is read by a MicroBlaze processor when the std\_counter reaches the maximum value. This process is repeated for subsequent ROs in the same configuration and frequencies are found. Adjacent ROs must be used for pairwise comparisons to eliminate the effects of systematic variations and also because the covariance is too small

[WHP14]. A Configurable RO consisting of N-ROs will produce a response of (N-1) bits.

Thus the design produces 256 IDs – one for each configuration with 63 bits each.

# 7.4. Advantages of the Proposed Design

- Increased number of configurations leads to increased number of CRPs,

- Increase in robustness,

- CRPs with higher number of unstable bits can be discarded to ensure high

value of steadiness and reliability.

Due to the large number of CRPs, the design can also be used as a one-time pad

for authentication and preventing repeatability attacks.

# 7.5. Results and Analysis

## 7.5.1. Data Collection

The proposed PUF design was implemented on Spartan6 FPGAs (Nexys3 boards) with 64 ring-oscillators. The design was tested on 20 boards and the frequency data was collected for 10 samples each. The differences between adjacent frequencies were taken to calculate the identifier from the PUF response.

# 7.5.2. Datasets

The characteristics of the datasets analyzed are given in Table 2.

| Parameters/Dataset        | Maiti et. al | Xin et al. | Bilal et al. | Proposed<br>CRO |

|---------------------------|--------------|------------|--------------|-----------------|

| N (number of chips)       | 193          | NA         | 32           | 20              |

| M (number of ROs)         | 512 ROs      | 64 CROs    | 130 CROs     | 64 CROs         |

| K (number of identifiers) | 1            | 2          | 1            | 1               |

| L (length of response)    | 511          | 63         | 1032         | 63              |

| T (number of samples)     | 100          | NA         | 20           | 10              |

Table 2. Datasets analyzed

## 7.5.3. Evaluation of Metrics

The datasets for the PUF implementations were evaluated using Python scripts based on the definitions provided in [MS11]. The metrics obtained for the three PUF implementations are tabulated in Table 3 to enable easy comparison.

| Metric                       | Ideal<br>value<br>(%) | Calculated Values (in %) |                       |                     |                 |  |

|------------------------------|-----------------------|--------------------------|-----------------------|---------------------|-----------------|--|

| Metric                       |                       | [Mai12]                  | Bilal -<br>horizontal | Bilal –<br>Vertical | Proposed design |  |

| Uniqueness<br>– Maiti et al. | 50                    | 47.236                   | 48.3                  | 47.67               | 45.372          |  |

| Uniqueness<br>– Hori et al.  | 100                   | 93.983                   | -                     | -                   | 91.598          |  |

| Bit –<br>Aliasing            | 50                    | 50.56                    | 51.8                  | 50.75               | 46.711          |  |

| Uniformity                   | 50                    | 50.56                    | 50.13                 | 50.75               | 46.711          |  |

| Randomness                   | 100                   | 94.948                   | -                     | -                   | 91.320          |  |

| Reliability                  | 100                   | 99.13                    | 97.88                 | 98.1                | 99.123          |  |

| Correctness                  | 100                   | 98.26                    | -                     | -                   | 98.450          |  |

| Steadiness                   | 100                   | 98.503                   | 99.5                  | 99.5                | 94.602          |  |

Table 3. Comparison of Metrics of predecessor designs with proposed design

Thus, the implemented RO-PUF design has a higher uniqueness value compared to [HGK13] and is comparable to that of [Mai12]. Also, the number of CRPs obtained by this method is higher compared to [Mai12], thus more reliable IDs can be generated for the same area consumed.

# 8. A NOVEL PROPOSAL FOR POST-PROCESSING OF PUF RESPONSES

## 8.1. **Biometrics**

A biometric feature is described as a physiological or behavioral characteristic that can be measured to confirm the identity of an individual [DCGM07]. Biometrics are classified as

- a. Physical Biometric if the physical characteristics of an individual like fingerprint, iris, facial features are used for identification or

- b. Behavioral Biometric wherein the behavioral characteristics like voice, handwriting, gait, etc. form the basis of identification.

# 8.2. Artificial Neural Networks

Artificial Neural Networks (ANN) emulate the functioning of biological neural networks. This, in biological terms would be 'to learn' based on conditions and experiences. An ANN is an adaptive non-linear system that learns to perform a function based on data. The training phase enables the tuning of the input parameters based on the system conditions. The learning rule is to optimize the performance criterion by a systematic procedure. The testing phase deploys the problem at hand to be solved based on the parameters that are 'learnt' during the training phase.

# 8.3. Hidden Markov Models

Hidden Markov Models are mainly used for statistical pattern recognition. Their effective self-organizing learning capabilities and time-warping capabilities have led

them to be used in the state-of-the-art behavioral recognition systems like speech recognition, handwriting recognition [Dol98]. A Hidden Markov Model (HMM) [RJ86] is a stochastic model used for modelling the structure of an observation sequence with a high level of flexibility. Each observation is paired with a (hidden) state (probability density function) and this enables easy recovery of the (hidden) structure of a sequence of observations.

The Markov property states that the transition at each step depends only on the previous transition. A HMM follows the Markov property with hidden states and visible outcomes. The inputs to a HMM are a sequence of observations, and for each outcome, the computation consists of determining a path of state transitions which is the most probable among all paths to produce the given observations.

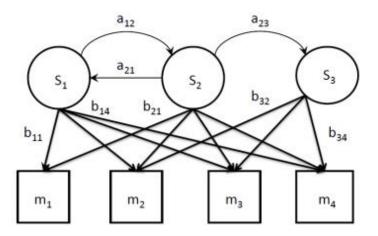

Figure 25. Hidden Markov Model

A HMM [AB13], as shown in Fig. 25 consists of

- a. N states denoted by S

- b. M possible outcomes denoted by m

- c. Initial state probability distribution vector (pi)

- d. State transition probability matrix (N x N) cells denoted by aij

- e. Output probability matrix (N x M) cells denoted by bij

The Forward Algorithm, Viterbi Algorithm and Expected Maximum (EM) Algorithms are used for dynamic programming of HMM computation to compute the most likely path based on the observations.

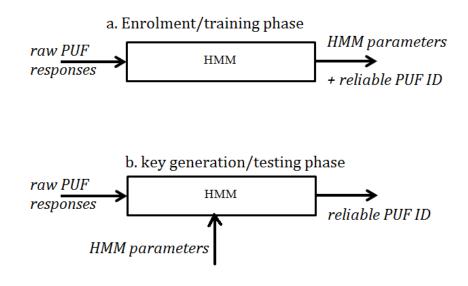

## 8.4. Proposal for Post-Processing